# **TMC2360**

# Video Output Processor VGA to NTSC/PAL

### **Features**

- · Single-package graphics to video conversion

- Multiple input formats

- 640x480 50/60 Hz, 800x600 50 Hz

- Multiple output standards

- NTSC, NTSC-EIA, PAL-B/G/H/I, PAL-M

- Composite and S-video output formats

- · No external memory required

- · Horizontal and vertical positioning inputs

- Configuration set by 11 switches

- Microcontroller port optional

- Auto sync polarity detection

- · Internal color bars

- 3-channel 8-bit input digitizer

- 2x oversampling 9-bit D/A converters

- Accepts programming through H and V timing

VESA DPMS, filter modes, video standard

- Single +5V power supply

# **Applications**

- VGA to video converter modules

- · Computer video outputs

- · Video games

- · TV VGA in

# **Description**

The TMC2360 converts RGB video and sync from a standard VGA source into NTSC or PAL video. Composite and S-Video outputs are compliant with SMPTE-170M and CCIR-656 specifications. A fully-integrated 3-line flicker filter provides three selectable operating modes.

Reference designs are available from the factory. System implementation requires an absolute minimum of external components. Critical timing is derived from a single 27 MHz crystal or an external clock reference.

All functions are directly controlled via package pins. Video and filtering modes may be programmed through either a microcontroller port or Vertical Sync Communications (VSCOM). VESA Display Power Management Signaling (DPMS) is supported.

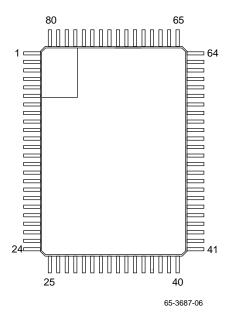

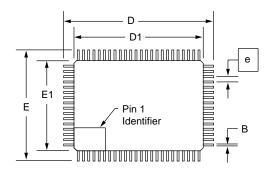

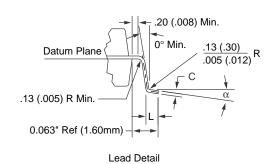

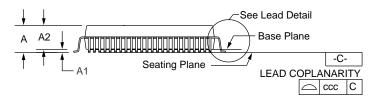

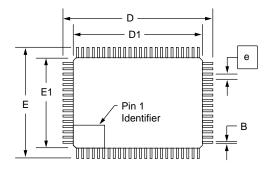

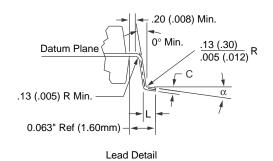

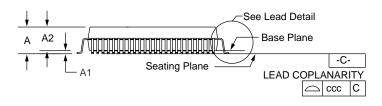

Power is derived from a single +5V supply. Package is an 80-lead Metric Quad Flat Pack (MQFP), available in 2.0mm (KM) or 2.7mm (KL) package thickness.

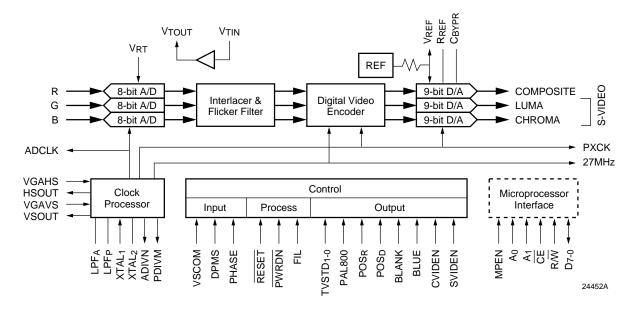

# **Block Diagram**

# **Functional Description**

The TMC2360 is a VGA to Video converter capable of producing video signals conforming to NTSC and PAL standards using a single low-cost application circuit. Within the TMC2360 is all of the active circuitry required to generate a television signal with outstanding image quality in a standalone application.

Incoming VGA source signals must be 2X the frame and 2X the line rate of the outgoing TV standard within a  $\pm 2\%$  tolerance. Supported VGA formats are 640x480 at 60 Hz for NTSC and PAL-M, and 640x480 and 800x600 at 50 Hz for PAL B/G/H/I.

The TMC2360 is ideal for portable converter applications, as well as integration into notebook and palmtop computers and video games.

# **Input Section**

Analog VGA signals are digitized by three 8-bit A/D converters, operating at rates of up to 36 Ms/s. The signal range is 0 to 700 mV established by the reference voltage, VRT.

By connecting VTOUT to VRT, the A/D converter reference voltage may be supplied by an on-chip voltage follower with an input, VTIN, that may be varied from 0 to 2 volts to accommodate different input levels.

#### **Clock Processor**

Two phase-locked loops synthesize clocks from the VGA Horizontal Sync signal. One loop generates ADCLK, which is used internally as the A/D sample clock. A second PLL generates PXCK, which is used internally as the digital encoder clock.

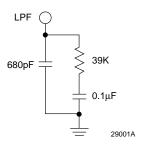

Either internal or external phase-locked loops may be selected by programming pins A<sub>1</sub> and A<sub>0</sub>. For internal loops, loop filters must be connected to LPFA and LPFP.

With external phase-locked loops, the internal divide by N and divide by M counters are still used. Only the phase detector, charge pump and VCO need be located in the external controller.

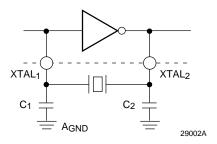

A stable timebase reference for subcarrier generation is derived from a 27 MHz crystal, or a TTL clock applied to pin XTAL<sub>1</sub>.

To synchronize the video encoder, vertical timing is derived from VGAVS, the VGA vertical sync signal. VGAHS and VGAVS signals of either polarity are accepted.

VESA Display Power Management Signaling functions may be enabled with the DPMS pin. Using the DPMS protocol, operational commands may be communicated to the TMC2360 via VGAHS and VGAVS signals. DPMS STAND-BY or DPMS SUSPEND modes set the processor to sleep and blanks the screen. DPMS OFF sets the processor, A/Ds and D/As to sleep with a blanked screen.

Vertical Sync Communications may be enabled with the VSCOM pin to detect the number of VGAHS pulses during the VGAVS period. With VSCOM, the Flicker Filter mode and the Video Standard may be selected by commands communicated via the VGA sync signals.

#### Flicker Filter

Flicker may be traded-off against vertical resolution with a three-line adaptive flicker filter. A single toggle pin (FIL) selects either High Filter, Medium Filter, or No Filter modes. A fourth mode, Color Bars, is useful for video setup and as a reference point for filter selection.

#### Video Encoder

Unless VSCOM is enabled, TVSTD<sub>1-0</sub> pins select the TV standard to be either NTSC, PAL or PAL-M.

Relative to the bezel framed by horizontal and vertical sync, the image may be moved right/left, and down/up by pulsing the POS<sub>R</sub> and POS<sub>D</sub> pins. BLANK suppreses the image, setting the screen either black or blue according to the state of the BLUE pin.

NTSC (SMPTE 170M) and PAL (CCIR 624) video signals are produced by three 9-bit D/A converters that can drive the  $37.5\Omega$  load of a double-terminated  $75\Omega$  line. Digital 2X oversampling minimizes  $\sin X/X$  distortion, facilitating use of low-cost output filters.

Composite and S-Video D/As are independently enabled via CVIDEN and SVIDEN pins to minimize power dissipation.

### **Control Processor**

TMC2360 setup and control is derived from external switches and push buttons. Schmitt trigger inputs reject external noise. Unused controls may be preset by hardwiring inputs to ground or V<sub>CC</sub>.

#### **Encoder Output Current**

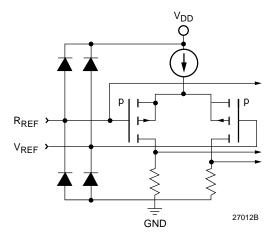

Output current is established by  $V_{REF}$  and an external resistor connected between  $R_{REF}$  and ground. An internal 1.235 volt reference is buffered from  $V_{REF}$  by a resistor, so  $V_{REF}$  may be overridden by an external voltage. Output current may be calibrated by resistor selection or setting a potentiometer attached to  $R_{REF}$ .

To minimize DAC noise, a bypass capacitor must be connected from CBYPR to an adjacent VDDA pin.

#### **Microprocessor Port**

Instead of utilizing control pin inputs, two operational modes, TV Standard and Flicker Filter, may be selected by writing to the VGA control register. Five registers may be read: address, VGA0, VGA1, Revision ID and Part ID.

# Pin Assignments – 80-Lead MQFP Package (KL or KM)

| Pin | Name             | Pin | Name               | Pin | Name              | Pin | Name              |

|-----|------------------|-----|--------------------|-----|-------------------|-----|-------------------|

| 1   | AGND             | 21  | D <sub>4</sub>     | 41  | PAL800            | 61  | DGND              |

| 2   | COMPOSITE        | 22  | D <sub>3</sub>     | 42  | FIL               | 62  | $V_{DD}$          |

| 3   | R <sub>REF</sub> | 23  | D <sub>2</sub>     | 43  | DPMS              | 63  | AGND              |

| 4   | V <sub>REF</sub> | 24  | D <sub>1</sub>     | 44  | VSCOM             | 64  | LPFA              |

| 5   | DGND             | 25  | D <sub>0</sub>     | 45  | VGAVS             | 65  | VDDPLLA           |

| 6   | PHASE            | 26  | VSOUT              | 46  | VGAHS             | 66  | AGND              |

| 7   | V <sub>DD</sub>  | 27  | HS0UT              | 47  | P0S <sub>R</sub>  | 67  | LPFp              |

| 8   | DGND             | 28  | DGND               | 48  | POSD              | 68  | VDDPLLP           |

| 9   | $V_{DD}$         | 29  | $V_{DD}$           | 49  | AGND              | 69  | XTAL <sub>2</sub> |

| 10  | DGND             | 30  | MPEN               | 50  | В                 | 70  | XTAL <sub>1</sub> |

| 11  | 27MHZ            | 31  | A <sub>1</sub>     | 51  | $V_{DDA}$         | 71  | RESET             |

| 12  | PXCK             | 32  | A <sub>0</sub>     | 52  | $V_{DDA}$         | 72  | PWRDN             |

| 13  | ADCLK            | 33  | R/W                | 53  | G                 | 73  | SVIDEN            |

| 14  | V <sub>DD</sub>  | 34  | CE                 | 54  | AGND              | 74  | CVIDEN            |

| 15  | DGND             | 35  | V <sub>DD</sub>    | 55  | VRT               | 75  | V <sub>DDA</sub>  |

| 16  | ADIVN            | 36  | DGND               | 56  | V <sub>TOUT</sub> | 76  | $V_{DDA}$         |

| 17  | PDIVM            | 37  | BLUE               | 57  | V <sub>TIN</sub>  | 77  | CBYPR             |

| 18  | D <sub>7</sub>   | 38  | BLANK              | 58  | AGND              | 78  | CHROMA            |

| 19  | D <sub>6</sub>   | 39  | TVSTD <sub>1</sub> | 59  | R                 | 79  | AGND              |

| 20  | D5               | 40  | TVSTD <sub>0</sub> | 60  | V <sub>DDA</sub>  | 80  | LUMA              |

# **Pin Descriptions**

| Pin Name            | Pin Number | Type/<br>Value    | Pin Function Description                                                                                                                                                                                                                  |

|---------------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks              | •          |                   |                                                                                                                                                                                                                                           |

| ADCLK               | 13         | TTL               | A/D Converter Clock Output. Generated by an internal phase-locked loop slaved to VGAHS.                                                                                                                                                   |

| ADIVN               | 16         | TTL               | Internal ADCLK divided by N Output. Enabled by A <sub>0</sub> and A <sub>1</sub> pins according to Table 1 or by VGA Control Register 1.                                                                                                  |

| LPFA                | 64         | _                 | A/D PLL Loop Filter Connection. An external RC network is connected here.                                                                                                                                                                 |

| PXCK                | 12         | TTL               | <b>Encoder Clock Output.</b> Generated by an internal phase-locked loop slaved to VGAHS.                                                                                                                                                  |

| PDIVM               | 17         | TTL               | Internal PXCK divided by M Output. Enabled by A <sub>0</sub> and A <sub>1</sub> pins according to Table 1 or by VGA Control Register 1.                                                                                                   |

| LPF <sub>P</sub>    | 67         | _                 | <b>Encoder PLL Loop Filter Connection.</b> An external RC network is connected here.                                                                                                                                                      |

| XTAL <sub>1-2</sub> | 70, 69     | _                 | Subcarrier Reference Crystal/Clock. Connection terminals for an external 27 MHz crystal. Alternatively, the XTAL1 pin may be used as an input from an external oscillator or clock. Subcarrier frequency accuracy is based on this clock. |

| 27MHZ               | 11         | TTL               | Subcarrier Reference Clock Output. Buffered TTL output from 27MHz crystal oscillator/reference clock.                                                                                                                                     |

| VGAHS               | 46         | CMOS <sub>S</sub> | VGA Horizontal Sync. Incoming VGA sync may be of either polarity (active LOW or active HIGH). VGAHS frequency must be within 2% of the nominal specified value. The VGAHS pin has a light pull-up and a Schmitt trigger.                  |

# Pin Descriptions (continued)

| Pin Name             | Pin Number | Type/<br>Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                         |  |

|----------------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VGAVS                | 45         | CMOSs          | VGA Vertical Sync. Incoming VGA sync may be of either polarity (active LOW or active HIGH). The VGAVS pin has a light pull-up and a Schmitt trigger.                                                                                                                                                                                                             |  |

| HSOUT                | 27         | TTL            | Buffered Horizontal Sync Output. Follows VGAHS.                                                                                                                                                                                                                                                                                                                  |  |

| VSOUT                | 26         | TTL            | Buffered Vertical Sync Output. Follows VGAVS.                                                                                                                                                                                                                                                                                                                    |  |

| Global Conti         | rols       |                |                                                                                                                                                                                                                                                                                                                                                                  |  |

| TVSTD <sub>1-0</sub> | 39, 40     | CMOSP          | <b>Video Output Standard Select.</b> Preprogrammed into the TMC236 are timing, subcarrier frequency and phase parameters corresponding to worldwide NTSC and PAL standards. TVSTD <sub>1-0</sub> select one of four sets of parameters to set up the encoder. Frame rate of the graphics source must be twice the frame rate of the selected video standard.     |  |

| PAL800               | 41         | CMOSP          | <b>Resolution Select for PAL.</b> Sets number of samples per VGA line.                                                                                                                                                                                                                                                                                           |  |

| DPMS                 | 43         | CMOSP          | <b>Display Power Management Signaling Enable.</b> When HIGH, the operational state of the TMC2360 is controlled by the pulse activity on VGAHS and VGAVS. When LOW, the state of the TMC2360 is controlled only by input pins.                                                                                                                                   |  |

| FIL                  | 42         | CMOSs          | Flicker Filter Mode Select. The adaptive flicker reduction filter may be configured for HIGH filtering, MEDIUM filtering, or NO filtering by pulsing this input HIGH. FIL defaults to HIGH-filter mode upon powerup. If VSCOM is HIGH, the filter mode will be selected by the pulsewidth of VGAVS, and FIL will be ignored. The FIL input is a Schmitt trigger. |  |

| VSCOM                | 44         | CMOSP          | <b>Vertical Sync Communications Enable.</b> When HIGH, vertical sync pulse width (VGAVS) will control the filter mode, and FIL will be ignored.                                                                                                                                                                                                                  |  |

| PWRDN                | 72         | CMOSP          | Power-Down Control. When HIGH, the TMC2360 is fully operational and enabled. When LOW, the TMC2360 is configured for minimum power consumption. D/A converters and clocks are disabled. Previously established set-up conditions are retained and remain in effect when PWRDN goes HIGH.                                                                         |  |

| RESET                | 71         | CMOSP          | Reset. Initializes internal registers.                                                                                                                                                                                                                                                                                                                           |  |

| PHASE                | 6          | CMOSP          | <b>Sampling Phase Control.</b> Shifts the A/D sampling phase by 180°. Set Phase = LOW.                                                                                                                                                                                                                                                                           |  |

| Encoder Cor          | ntrols     |                |                                                                                                                                                                                                                                                                                                                                                                  |  |

| CVIDEN               | 74         | CMOSP          | Composite Video D/A Power Enable. When HIGH, the COMPOSITE D/A converter is enabled. When LOW it is disabled to save power.                                                                                                                                                                                                                                      |  |

| SVIDEN               | 73         | CMOSP          | <b>S-Video D/A Power Enable.</b> When HIGH, the CHROMA and LUMA D/A converters are enabled. When LOW, they are disabled to save power.                                                                                                                                                                                                                           |  |

| BLANK                | 38         | CMOSP          | Blank Screen Generator. When HIGH, the color selected by BLUE is displayed on the screen. When LOW, incoming video from the internal FIFO is encoded.                                                                                                                                                                                                            |  |

| BLUE                 | 37         | CMOSP          | Blank Screen Color Selector. When HIGH, the screen will be blanked to blue when BLANK is HIGH. When LOW, the screen will be blanked to black when BLANK is HIGH.                                                                                                                                                                                                 |  |

# Pin Descriptions (continued)

| Pin Name      | Pin Number  | Type/<br>Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POSR, D       | 47, 48      | CMOSs          | <b>TV Image Position Controls.</b> Position controls shift the VGA image horizontally or vertically, revealing portions that are found near the edges or in the overscan areas. Default power-up position is the midpoint of the adjustment range. POSD,R inputs are Schmitt triggers.                                                                                                                                      |

| A/D Converte  | r Interface |                |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R, G, B       | 59, 53, 50  | 700 mV         | <b>Analog RGB Inputs.</b> Analog red, blue and green inputs to the A/D converters from incoming VGA signals. Nominal voltage range is 0.0 to +700 mV.                                                                                                                                                                                                                                                                       |

| VTIN          | 57          | 750 mV         | A/D Converter Reference Buffered Input. Buffer is a voltage follower that may be connected to VRT.                                                                                                                                                                                                                                                                                                                          |

| Vтоит         | 56          | 750 mV         | <b>A/D Converter Reference Buffered Output</b> . May be connected to V <sub>RT</sub> to supply current to A/D converter reference resistors. In power down mode, V <sub>TOUT</sub> drops to zero.                                                                                                                                                                                                                           |

| VRT           | 55          | 750 mV         | A/D Converter Reference Input, Unbuffered. Supplies current to A/D converter reference resistors. May be driven from V <sub>TOUT</sub> . Voltage range is 0.5 to 2.0 volts.                                                                                                                                                                                                                                                 |

| Video Outputs | s           |                |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COMPOSITE     | 2           | 1 V p-p        | NTSC/PAL Video Output, Composite Video. NTSC/PAL baseband composite output can drive 1 Volt p-p video into a 37.5 $\Omega$ load. Contains sync, subcarrier and active video information to drive monitors, projectors, VCRs, and other video devices.                                                                                                                                                                       |

| LUMA          | 80          | 1 V p-p        | <b>Luminance-only Video.</b> This analog monochrome video output can drive 1 Volt p-p video into a 37.5 $\Omega$ load. Contains all sync and active video information necessary to drive black-and-white video devices.                                                                                                                                                                                                     |

| CHROMA        | 78          | 1 V p-p        | Chrominance-only Video. This analog output can drive a 37.5 $\Omega$ load. CHROMA signal, when combined with LUMA comprises an S-Video signal suitable for driving monitors, projectors, VCRs, and other S-Video devices.                                                                                                                                                                                                   |

| Voltage Refer | ence        |                |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VREF          | 4           | +1.23 V        | Voltage Reference Input/Output. Output of an internal 1.23 Volt band-gap voltage reference. If unconnected, except for a 0.1F capacitor to ground for noise decoupling, the internal reference will be used for the three D/A converters. An externally generated voltage reference of +1.2 Volts applied to the VREF pin will override the internal voltage reference and become the new reference for the D/A converters. |

| Свург         | 77          | 0.1 μF         | <b>Reference Bypass Capacitor.</b> An external 0.1F capacitor should be connected between CBYPR and VDDA to reduce noise on the internal reference circuitry.                                                                                                                                                                                                                                                               |

| RREF          | 3           | 392Ω           | Current-setting Resistor. A $392\Omega$ resistor connected between the RREF terminal and ground establishes the reference current for the three internal D/A converters. Resistor value determines the full-scale output current (and therefore the peak video level) of the D/A converters.                                                                                                                                |

# Pin Descriptions (continued)

| Pin Name        | Pin Number                        | Type/<br>Value | Pin Function Description                                                                                                                                                                                                                |

|-----------------|-----------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microproces     | ssor Interface                    |                |                                                                                                                                                                                                                                         |

| MPEN            | 30                                | TTL            | <b>Microprocessor Port Enable.</b> With MPEN = LOW, the port is disabled and control is via individual pins. With MPEN = HIGH, selected functions may be accessed through the microprocessor port.                                      |

| A <sub>0</sub>  | 32                                | TTL            | External PXCK Phase-locked Loop Select/Address Bit. Dual function pin. If MPEN = HIGH, A <sub>0</sub> is the microprocessor port address bit A <sub>0</sub> . If MPEN = LOW, A <sub>0</sub> configures the PXCK PLL inputs and outputs. |

| A1              | 31                                | TTL            | External ADCLK Phase-locked Loop Select. If MPEN = LOW, A1 configures the ADCLK PLL inputs and outputs.                                                                                                                                 |

| R/W             | 33                                | TTL            | Read/Write. Read/Write selects the direction of the 8-bit data bus.                                                                                                                                                                     |

| CE              | 34                                | TTL            | <b>Chip Enable.</b> When $\overline{CE} = H$ , $D_{7-0}$ are high impedance. When $\overline{CE} = L$ , $R/\overline{W}$ sets $D_{7-0}$ to either the read or write state.                                                              |

| D7-0            | 18, 19, 20, 21,<br>22, 23, 24, 25 | TTL            | <b>Data bits.</b> Data bus is high impedance unless $\overline{CE} = L$ and $R/\overline{W} = H$ .                                                                                                                                      |

| Power and 0     | Ground                            |                |                                                                                                                                                                                                                                         |

| V <sub>DD</sub> | 7, 9, 14, 29,<br>35, 62,          | +5.0 V         | <b>Digital Power Supply.</b> Supplies +5V power to internal digital circuits.                                                                                                                                                           |

| VDDA            | 51, 52, 60, 75,<br>76             | +5.0 V         | Analog Power Supply. Supples +5V power to internal analog circuits. VDD and VDDA must originate from the same source.                                                                                                                   |

| VDDPLLA         | 65                                | +5.0 V         | <b>A/D Phase Locked Loop +5V Power.</b> VDDPLLA and VDD must originate from the same source.                                                                                                                                            |

| VDDPLLP         | 68                                | +5.0 V         | <b>Encoder Phase Locked Loop +5V Power.</b> VDDPLLP and VDD must originate from the same source.                                                                                                                                        |

| DGND            | 5, 8, 10, 15,<br>28, 36, 61       | 0.0 V          | Digital Ground. Ground point for internal digital circuits.                                                                                                                                                                             |

| AGND            | 1, 49, 54, 58,<br>63, 66, 79      | 0.0 V          | <b>Analog Ground.</b> Ground point for internal analog circuits. DGND and AGND should be connected to the same ground plane.                                                                                                            |

# Notes:

CMOSP = CMOS with light pull-up CMOSS = CMOS with Schmitt Trigger

6

### **Clocks**

There are three internal clocks, ADCLK, PXCK, and 27MHz. ADCLK is the clock for the A/D converters with sampling on the edge selected by PHASE. PXCK is the encoder clock for sequencing data to the D/A converters at a 2X rate. 27MHz is the reference clock from which the chroma subcarrier data is synthesized.

ADCLK and PXCK clocks may be derived from internal or external phase-locked loops. Only an external controller containing the phase detector, charge pump, and VCO is needed for each loop. An internal divider programmed with the correct counts is included within the TMC2360.

Control of the internal/external PLL modes is either via the  $A_0$  and  $A_1$  pins (see Table 1) or through the VGA1 Control register, which can be programmed via the microprocessor port.

With control via A<sub>0</sub> and A<sub>1</sub> pins, the outputs PDIVM and ADIVN are high impedance unless either PLL is programmed to be external. A<sub>0</sub> and A<sub>1</sub> also control the direction of the ADCLK and PXCK clock pins. Each clock (ADCLK and PXCK) is an output in the internal mode and an output in the external mode.

Table 1. Internal/External Phase-locked Loop Selection (MPEN = L)

| A1 | A <sub>0</sub> | PLLA     | PLLP     | ADIVN  | PDIVM  | ADCLK  | PXCK   |

|----|----------------|----------|----------|--------|--------|--------|--------|

| 0  | 0              | Internal | Internal | High-Z | High-Z | Output | Output |

| 0  | 1              | Internal | External | 1/N    | 1/M    | Output | Input  |

| 1  | 0              | External | Internal | 1/N    | 1/M    | Input  | Output |

| 1  | 1              | External | External | 1/N    | 1/M    | Input  | Input  |

### A/D Clock (ADCLK)

ADCLK is the buffered analog-to-digital converter clock output which is derived from incoming VGA horizontal sync (VGAHS) by a phase-lock loop (PLL). Either an internal PLL or an external PLL controller may be selected by programming pin  $A_1$ .

A/D Clock frequency is set by the PLL divide-by-N counter where N is the number of A/D samples between the horizontal sync pulses in each VGA line.

Pre-programmed values selected by the TVSTD<sub>1-0</sub> and PAL800 control inputs set N and the clock frequency as shown in Table 2.

Table 2. VGA A/D Clock

| Television<br>Standard | TVSTD <sub>1-0</sub> | PAL800 | ADCLK<br>Freq. (MHz) | N    |

|------------------------|----------------------|--------|----------------------|------|

| NTSC                   | 0x                   | 0      | 25.175               | 800  |

| PAL640                 | 10                   | 0      | 25.250               | 808  |

| PAL800                 | 10                   | 1      | 36.000               | 1152 |

| PALM                   | 11                   | 0      | 25.175               | 800  |

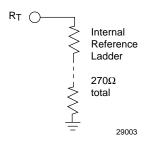

For an internal loop, the recommended loop filter to be connected to the LPF<sub>A</sub> pin is shown in Figure 1.

Figure 1. PLL Low Pass Filter

### **Pixel Clock (PXCK)**

PXCK is the buffered video encoder clock output which is derived from the incoming VGA HSYNC signal by a second phase-lock loop. Either an internal PLL or an external PLL controller may be selected by programming pin A<sub>0</sub>.

With the internal loop selected, Figure 1 shows the recommended loop filter, which should be connected to LPFP.

Clock frequency is set by the PLL divide-by-M counter. M is the number of encoder samples between horizontal sync pulses. Because of 2X oversampling, the pixel rate is twice the TV square pixel rate. Table 3 shows the video output clock rates and M values.

| Table 3  | NTSC    | and PAL | Pival | Clacks |

|----------|---------|---------|-------|--------|

| Table 5. | 14 1 20 | and FAL | CIXCI | CHURA  |

| Television<br>Standard | Line Rate<br>(kHz) | Pixel Rate<br>(MHz) | М   |

|------------------------|--------------------|---------------------|-----|

| NTSC                   | 15.734             | 24.545              | 780 |

| PAL                    | 15.625             | 29.500              | 944 |

| PALM                   | 15.750             | 24.570              | 780 |

#### **Reference Clock**

Accuracy of the PAL/NTSC subcarrier depends on the 27 MHz reference signal applied to the XTAL1. This signal may be derived from a clock connected directly to the XTAL1 pin or a crystal and capacitors connected across XTAL1-2 as shown in Figure 2.

Figure 2. Crystal Oscillator Circuit

Capacitors C<sub>1</sub> and C<sub>2</sub> must be adjusted to trim the frequency within 20 ppm. C<sub>1</sub> and C<sub>2</sub> have the same value, with series capacitance equal to the load recommended for the crystal.

Typical crystal parameters are 50 ppm accuracy with a 20 pF load and  $\pm 80$  ppm pullability.

# **Digitizing**

#### A/D Reference

An on-chip voltage follower is included to supply current to the ADC reference VRT from VTOUT. A stable voltage source greater than the input peak amplitude should be connected to VTIN.

#### **Input Signal Conditioning**

ADC performance can be optimized by driving the RGB video inputs with either a 75 ohm or a low impedance source.

#### Input Format Selection

One of four input VGA formats can be accepted by setting the  $TVSTD_{1-0}$  and PAL800 inputs as shown in Table 4. Each VGA input option corresponds to a VGA active video area, frame rate and line rate with a corresponding TV output format.

**Table 4. VGA Input Formats**

| TVSTD <sub>1-0</sub> | PAL800 | H x V<br>Input<br>Pixels | Frame<br>Rate<br>(Hz) | Line<br>Rate<br>(kHz) |

|----------------------|--------|--------------------------|-----------------------|-----------------------|

| 0x                   | 0      | 640 x 480                | 59.94                 | 31.469                |

| 10                   | 0      | 640 x 480                | 50                    | 31.250                |

| 10                   | 1      | 800 x 600                | 50                    | 31.250                |

| 11                   | 0      | 640 x 480                | 60                    | 31.469                |

# **Processing**

#### Flicker Filter

Annoying artifacts can be eliminated by selecting one of three filter modes, which trade-off vertical resolution against flicker. Without the filter, one contrasting VGA line may be encoded into one field of the TV video, which will flicker at 30 Hz with NTSC and 25 Hz with PAL.

As shown in Table 5, if VSCOM = LOW, pulsing the FIL pin indexes the TMC2360 through a loop of three filter modes and a color bar pattern.

**Table 5. FIL Filter Mode Select Sequence**

| FIL        | Filter Mode    |

|------------|----------------|

| <b>↓ ▲</b> | HIGH (default) |

| <b>1</b>   | MEDIUM         |

| <b>1</b>   | No filter      |

|            | Color bars     |

### Video Encoder

#### D/A Reference

Peak D/A converter current for the video outputs is set by a resistor connected to  $R_{REF}$ . For 1 volt video, with a 37.5 ohm load, the correct value of  $R_{REF}$  is 392 ohm. To trim the video output level,  $R_{REF}$  can be replaced with a potentiometer. (See the Applications Circuit, Figure 15).

#### **Television Standard Selection**

NTSC and PAL standards are preprogrammed into the TMC2360 to preset horizontal and vertical timing, subcarrier frequency, and chrominance phase. Frame rate of the VGA source must match the field rate of the selected video standard.

Depending upon the status of the Vertical Sync Communications (VSCOM) pin, the video output format may be selected by either the TVSTD1-0 pins or by VSCOM codes.

Table 6 shows how the  $TVSTD_{1-0}$  pins select the TV output format with VSCOM = LOW.

Table 6. TVSTD Control When Under Manual Control (VSCOM = 0)

| TVSTD <sub>1-0</sub> | Television<br>Standard | Video Field Rate |

|----------------------|------------------------|------------------|

| 01                   | NTSC                   | 59.94 Hz         |

| 00                   | NTSC-EIA               | 59.94 Hz         |

| 10                   | PAL/B, G, I            | 50 Hz            |

| 11                   | PAL/M                  | 60 Hz            |

If VCSOM = HIGH, Vertical Sync Communications are enabled. VSCOM is described under the Vertical Sync Command section below.

### **Image Positioning**

POSD and POSR position controls change encoder timing relative to incoming PC video, shifting the viewed image either horizontally or vertically to reveal portions of the image located near the edges or in the overscan areas. At power-up, the default position is the midpoint of the adjustment range.

Each POSD HIGH pulse moves the TV window down eight lines. At the lowest position (-64 lines) the direction reverses and the pulses move the image up in 8-line increments to the highest position (+64 lines). At this point the direction again reverses and the next sixteen pulses move the image down to the lowest position.

Each POSR HIGH pulse moves the TV window eight pixels to the right. At the maximum right position (+64 pixels) the direction reverses and the next sixteen pulses move the window left to the maximum left position (-64 pixels). Direction again reverses and the next sixteen pulse move the image right.

Without a RESET, POSD,R controls will loop, causing the window to move down/up, right/left.

#### Blank and Blue

TV video can set to active (converted VGA source), blank or blue by the BLANK and BLUE inputs.

Table 7. Video Output for BLANK and BLUE inputs

| BLANK | BLUE | Video |

|-------|------|-------|

| L     | X    | Video |

| Н     | L    | Black |

| Н     | Н    | Blue  |

# **Power Management**

### **D/A Power Control**

Table 8 shows how the Composite and S-video outputs are enabled by the CVIDEN and SVIDEN controls. If

DPMS = LOW, the display will be blue if either or both VGAHS or VGAVS are inactive.

**Table 8. Video Output Control**

| CVIDEN | SVIDEN | VGAHS & VGAVS | Compos-<br>ite Video | S-Video |

|--------|--------|---------------|----------------------|---------|

| Н      | Х      | YES           | Active               | Х       |

| Х      | Н      | YES           | Χ                    | Active  |

| L      | L      | Х             | Blank                | Blank   |

| Н      | Н      | NO            | Blue                 | Blue    |

#### **Powerdown Mode**

PWRDN eliminates current drain by the D/A converter, VTOUT voltage follower and clock outputs. With PWRDN = HIGH, all outputs are enabled. If PWRDN = LOW, all outputs are disabled including the ADCLK, PXCK, VTOUT and the D/A converters.

### **Software Control**

# **Display Power Management Signaling (DPMS)**

Display Power Management is compliant with VESA DPMS Proposal 1.0. With DPMS = HIGH, the operational state of the TMC2360 is controlled by the pulse activity on VGAHS and VGAVS.

Table 9 shows how the TMC2360 responds. "No Pulses" on VSYNC or HSYNC is declared on the second missing VSYNC or HSYNC pulse. Following an OFF state, detection of VGAHS and/or VGAVS restores either the Suspend, Standby, or On state.

Regardless of the state of DPMS, absence of VGAHS and/or VGAVS pulses will cause the TMC2360 processor to sleep. However, with DPMS = HIGH, in the Off state, the A/Ds, D/As, and clocks are also set to sleep.

#### **Vertical Sync Communications (VSCOM)**

VSCOM is a unique feature incorporated into the TMC2360. With VSCOM = HIGH, the TMC2360 interprets commands that are encoded within the VGA vertical sync period. TV Standard and Flicker Filter may be selected by commands from the PC that supplies the VGA signal.

During the vertical sync period, the number of horizontal sync pulses is counted. Table 10 shows how the selected Television Standard changes with the code set into the TVSTD<sub>1-0</sub> inputs and the number of horizontal syncs per vertical sync interval.

Table 11 shows how the Filter Mode is selected with VSCOM. Notice that if one standard, such as PAL800 is selected, then counts of 10, 11 and 12 enable selection of three filter modes.

| State    | VGAHS     | VGAVS     | TMC2360 State                                                                              |

|----------|-----------|-----------|--------------------------------------------------------------------------------------------|

| On       | Pulses    | Pulses    | On, video active                                                                           |

| Stand-by | No Pulses | Pulses    | Stand-by, screen blanked (color set by BLUE)                                               |

| Suspend  | Pulses    | No Pulses | Stand-by, screen blanked (color set by BLUE)                                               |

| Off      | No Pulses | No Pulses | Off, screen black (equivalent to PWRDN, except A/D Clock and 27MHZ oscillator are active.) |

Table 10. TVSTD Control When Under Software Control (VSCOM = 1)

| TVSTD <sub>1-0</sub> | Hsyncs per Vsync Interval | Television Standard         | VGA Frame Rate |

|----------------------|---------------------------|-----------------------------|----------------|

| XX                   | 10,11,12                  | PAL 800 (B, G, I)           | 50 Hz          |

| X0                   | 6,7,9                     | PAL 640 (B, G, I)           | 50 Hz          |

| 01                   | 6,7,9                     | PAL-M                       | 60 Hz          |

| 11                   | 6,7,9                     | (reserved)                  |                |

| 0X                   | 1-5,8,14,15               | NTSC-EIAJ                   | 60 Hz          |

| 10                   | 1-5,8,14,15               | NTSC                        | 60 Hz          |

| 11                   | 1-5,8,14,15               | (reserved)                  |                |

| XX                   | 0,13                      | Blank (with prior standard) | 50/60 Hz       |

Table 11. VSCOM Filter Command Interpretation (VSCOM=1)

| HSYNCs per VSYNC<br>Interval | Filter Mode             |

|------------------------------|-------------------------|

| 5, 9, 12                     | No Filter               |

| 4, 7, 11                     | 2-line filter           |

| 1, 2, 3, 6, 8, 10, 14, 15    | 3-line filter           |

| 0, 13                        | Blank (with prior mode) |

# **Microprocessor Interface**

Table 12 shows the five registers that may be read after the Address Register has been loaded. Only the two VGA registers and the Address Register may be written. For microprocessor control, 40h must be written into VGA register 1. To disable control through VGA Register 0, 00h must be written into register 1. Bit assignments of VGA register 0 are listed in Table 13. Bit assignments of VGA register 1 are listed in Table 14.

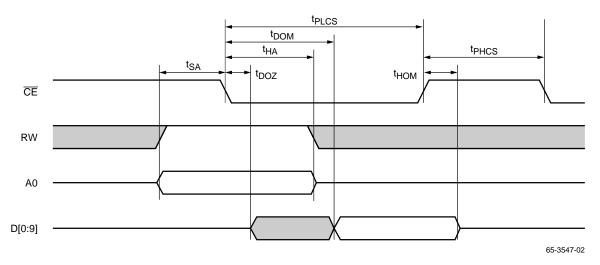

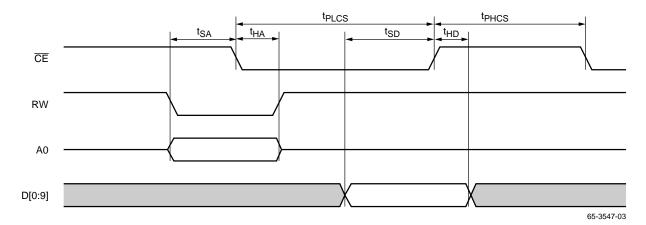

For communications through the microprocessor port, set MPEN = HIGH. Read and write timing is shown in Figure 3 and Figure 4. To access a VGA register, write the address of the selected register into the lower four bits of the eight bit Address Register with  $A_0 = LOW$ . Then with  $A_0 = HIGH$ , read or write to the selected register.

**Table 12. Microprocessor Addressable Registers**

| A1 | Α0 | Address<br>Register Value | Register          |

|----|----|---------------------------|-------------------|

| 0  | 0  | x                         | Address Register  |

| 0  | 1  | x0                        | VGA Register 0    |

| 0  | 1  | x1                        | VGA Register 1    |

| 0  | 1  | x6                        | Revision ID (xxh) |

| 0  | 1  | x7                        | Part ID (0Fh)     |

Table 13. VGA Control Register 0 Bit Map

| Bit # | Name  | Function          |  |  |

|-------|-------|-------------------|--|--|

| 7     | _     | 0 (reserved)      |  |  |

| 6-5   | FIL   | 0 0 No Filter     |  |  |

|       |       | 0 1 2-line Filter |  |  |

|       |       | 1 x 3-line Filter |  |  |

| 4-2   | TVSTD | 000 NTSC-EIA      |  |  |

|       |       | 0 0 1 NTSC        |  |  |

|       |       | 010 PALM          |  |  |

|       |       | 0 1 1 PAL640      |  |  |

|       |       | 1xx PAL800        |  |  |

| 1-0   | VIDEO | 0 0 Black         |  |  |

|       |       | 01 Ramp           |  |  |

|       |       | 1 0 Color Bars    |  |  |

|       |       | 1 1 Normal        |  |  |

Table 14. VGA Control Register 1 Bit Map

| Bit # | Name    | Function                    |

|-------|---------|-----------------------------|

| 7     | _       | 0 (reserved)                |

| 6     | MODE    | 0 Normal                    |

|       |         | Bypass FIL and TVSTD  Pins  |

| 5-3   | _       | 0 (reserved)                |

| 2     | DIVMN   | 0 (reserved)                |

|       |         | 1 Enable ADIVN and PVIDM    |

| 1     | EXTPLL  | 0 Disable external PXCK PLL |

|       |         | 1 Enable external PXCK PLL  |

| 0     | EXTPLLA | 0 Disable external ACLK PLL |

|       |         | 1 Enable external ACLK PLL  |

# **Video Formats**

# **Incoming VGA Formats**

Table 15 and Table 16 show expected VGA Video input formats.

# **Outgoing TV Formats**

Table 16 shows the four different TV formats that may be selected as outputs by the TVSTD<sub>1-0</sub> inputs.

Table 17 and Table 18 show the Horizontal and Vertical Timing for the NTSC and PAL formats.

**Table 15. VGA Horizontal Timing Parameters**

| Television<br>Standard | TVSTD1-0 | PAL800 | Line Rate<br>(kHz) | Front Porch (pixels) | Horiz Sync<br>(pixels) | Back Porch (pixels) | Active Video (pixels) |

|------------------------|----------|--------|--------------------|----------------------|------------------------|---------------------|-----------------------|

| NTSC(-EIA)             | 0x       | 0      | 31.469             | 18                   | 96                     | 46                  | 640                   |

| PAL/B, G, I            | 10       | 0      | 31.250             | 18                   | 96                     | 54                  | 640                   |

| PAL/B, G, I            | 10       | 1      | 31.250             | 98                   | 96                     | 158                 | 800                   |

| PAL/M                  | 11       | 0      | 31.500             | 18                   | 96                     | 46                  | 640                   |

**Table 16. VGA Vertical Timing Parameters**

| Television<br>Standard | TVSTD <sub>1-0</sub> | PAL800 | Frame<br>Rate<br>(Hz) | Line<br>Rate<br>(kHz) | Full<br>Frame<br>(lines) | Front<br>Porch<br>(lines) | Vert.<br>Sync<br>(lines) | Vsync +<br>Back Porch<br>(lines) | Active Video<br>(lines) |

|------------------------|----------------------|--------|-----------------------|-----------------------|--------------------------|---------------------------|--------------------------|----------------------------------|-------------------------|

| NTSC(-EIA)             | 0x                   | х      | 59.94                 | 31.469                | 525                      | 13                        | 2-16                     | 32                               | 480                     |

| PAL/B, G, I            | 10                   | 0      | 50                    | 31.250                | 625                      | 61                        | 2-16                     | 84                               | 480                     |

| PAL/B, G, I            | 10                   | 1      | 50                    | 31.250                | 625                      | 1                         | 2-16                     | 24                               | 600                     |

| PAL/M                  | 11                   | х      | 60                    | 31.469                | 525                      | 13                        | 2-16                     | 32                               | 480                     |

# **Table 17. NTSC and PAL Horizontal Timing**

|                        |                    |                 |                       | •                       |                       |                          |                         |                         |                           |                     |

|------------------------|--------------------|-----------------|-----------------------|-------------------------|-----------------------|--------------------------|-------------------------|-------------------------|---------------------------|---------------------|

| Television<br>Standard | Field Rate<br>(Hz) | Lines per frame | Line<br>Rate<br>(kHz) | 2x pix<br>Rate<br>(MHz) | fSC<br>Freq.<br>(MHz) | Front<br>Porch<br>pixels | Horiz<br>Sync<br>pixels | Back<br>Porch<br>pixels | Active<br>Video<br>pixels | Line<br>H<br>pixels |

| NTSC                   | 59.94              | 525             | 15.734                | 24.545                  | 3.579                 | 18                       | 58                      | 58                      | 646                       | 780                 |

| PAL                    | 50.00              | 625             | 15.625                | 29.500                  | 4.433                 | 18                       | 70                      | 82                      | 774                       | 944                 |

| PALM                   | 60                 | 525             | 15.734                | 25.570                  | 3.576                 | 18                       | 58                      | 58                      | 646                       | 780                 |

# Table 18. NTSC and PAL Vertical Timing

| TV<br>Std | Field Rate<br>(Hz) | Lines per frame | Line Rate<br>(kHz) | Front Porch (lines) | Vertical Sync (lines) | Back Porch (lines) | Active Video (lines) |

|-----------|--------------------|-----------------|--------------------|---------------------|-----------------------|--------------------|----------------------|

| NTSC      | 59.94              | 525             | 15.734             | 3-3.5               | 3                     | 14-14.5            | 242.5                |

| PAL       | 50.00              | 625             | 15.625             | 2.5                 | 2.5                   | 21                 | 286.5                |

| PALM      | 60.00              | 525             | 15.750             | 3                   | 3                     | 14                 | 242.5                |

# **Timing Diagrams**

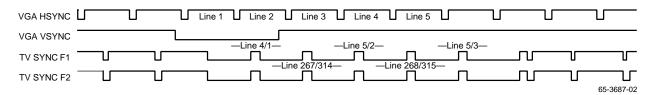

Figure 3. Nominal VGA-NTSC/PAL Vertical Sync Timing

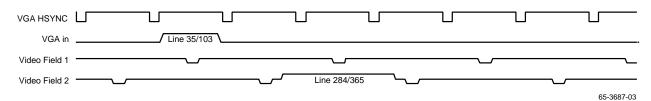

Figure 4. Nominal VGA640-NTSC/PAL, No Filter Timing

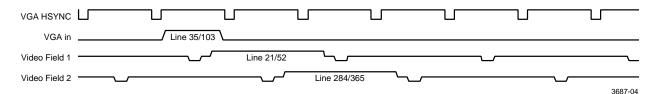

Figure 5. Nominal VGA-NTSC/PAL, Medium Filter Timing

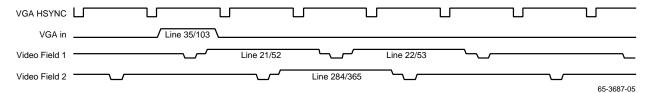

Figure 6. Nominal VGA-NTSC/PAL, High Filter Timing

# Timing Diagrams (continued)

Figure 7. Microprocessor Read Timing

Figure 8. Microprocessor Write Timing

# **Equivalent Circuits**

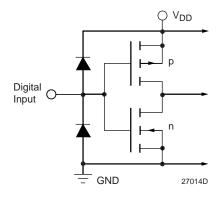

Figure 9. Equivalent Digital Input Circuit

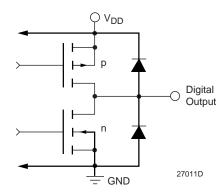

Figure 10. Equivalent Digital Output Circuit

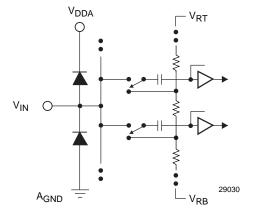

Figure 11. Equivalent A/D Input Circuit

Figure 12. Equivalent A/D Reference Input Circuit

Figure 13. Equivalent D/A Reference Input Circuit

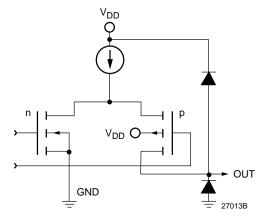

Figure 14. Equivalent D/A Output Circuit

# Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min.     | Тур. | Max.                  | Unit   |

|----------------------------------------------------------------|----------|------|-----------------------|--------|

| Power Supply Voltages                                          |          |      |                       |        |

| VDDA (Measured to AGND)                                        | -0.5     |      | 7.0                   | V      |

| V <sub>DD</sub> (Measured to DGND)                             | -0.5     |      | 7.0                   | V      |

| VDDA (Measured to VDD)                                         | -0.5     |      | 0.5                   | V      |

| AGND (Measured to DGND)                                        | -0.5     |      | 0.5                   | V      |

| Digital Inputs                                                 | •        |      |                       |        |

| Applied Voltage (Measured to DGND) <sup>2</sup>                | -0.5     |      | V <sub>DD</sub> + 0.5 | V      |

| Forced current <sup>3, 4</sup>                                 | -10.0    |      | 10.0                  | mA     |

| Analog Inputs                                                  | <u>'</u> |      | '                     |        |

| Applied Voltage (Measured to AGND) <sup>2</sup>                | -0.5     |      | VDDA + 0.5            | V      |

| Forced current <sup>3, 4</sup>                                 | -10.0    |      | 10.0                  | mA     |

| Digital Outputs                                                | '        |      | '                     |        |

| Applied Voltage (Measured to DGND) <sup>2</sup>                | -0.5     |      | V <sub>DD</sub> + 0.5 | V      |

| Forced current <sup>3, 4</sup>                                 | -6.0     |      | 6.0                   | mA     |

| Short circuit duration (single output in HIGH state to ground) |          |      | 1                     | second |

| Temperature                                                    |          |      |                       |        |

| Operating, Ambient                                             | -20      |      | 110                   | °C     |

| Junction                                                       |          |      | 150                   | °C     |

| Lead Soldering (10 seconds)                                    |          |      | 300                   | °C     |

| Vapor Phase Soldering (1 minute)                               |          |      | 220                   | °C     |

| Storage                                                        | -65      |      | 150                   | °C     |

| Electrostatic Discharge <sup>5</sup>                           |          |      | ±150                  | V      |

## Notes:

- 1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

- 5. EIAJ test method.

# **Operating Conditions**

| Paramet         | Parameter                                                                       |      | Nom.  | Max.            | Units |

|-----------------|---------------------------------------------------------------------------------|------|-------|-----------------|-------|

| VDD             | Digital Power Supply Voltage                                                    | 5.0  | 5.25  | V               |       |

| VDDA            | Analog Power Supply Voltage                                                     | 4.75 | 5.0   | 5.25            | V     |

| AGND            | Analog Ground (Measured to D <sub>GND</sub> )                                   | -0.1 | 0     | 0.1             | V     |

| VRT             | Reference Voltage, Top                                                          | 0.5  | 0.75  | 2.0             | V     |

| V <sub>IN</sub> | Analog Input Range                                                              | 0    |       | V <sub>RT</sub> | V     |

| VREF            | External Reference Voltage                                                      |      | 1.235 |                 | V     |

| IREF            | D/A Converter Reference Current (IREF = VREF/RREF, flowing out of the RREF pin) |      | 3.15  |                 | mA    |

| RREF            | Reference Resistor, VREF = Nom                                                  |      | 392   |                 | Ω     |

| Rout            | DAC Total Output Load Resistance                                                |      | 37.5  |                 | Ω     |

| TA              | Ambient Temperature, Still Air                                                  | 0    |       | 70              | °C    |

# **Electrical Characteristics**

| Parameter   | r                                     | Conditions                                    | Min.  | Тур.    | Max.  | Unit     |

|-------------|---------------------------------------|-----------------------------------------------|-------|---------|-------|----------|

| Power Sup   | pply Currents                         |                                               | !     | !       | !     | !        |

| IDD         | Operating                             | CVIDEN = H, SVIDEN = H                        |       | 300     | 400   | mA       |

| IDDS        | Standby                               | CVIDEN = L, SVIDEN = L                        |       | 100     |       | mA       |

| IDDQ        | Power-Down                            | PWRDN = L                                     |       |         | 5     | mA       |

| IDDSV       | S-Video Active                        | CVIDEN = L, SVIDEN = H                        |       | 250     | 350   | mA       |

| IDDCV       | Composite Video Active                | CVIDEN = H, SVIDEN = L                        |       | 200     | 270   | mA       |

| Digital Inp | outs and Outputs                      |                                               | !     | !       | !     |          |

| Cı          | Input Capacitance                     |                                               |       | 5       | 10    | pF       |

| Co          | Output Capacitance                    |                                               |       | 10      |       | pF       |

| lін         | Input Current, HIGH                   | VDD = Max, VIN = VDD                          |       |         | ±10   | μА       |

| IIL         | Input Current, LOW                    | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0 V  |       |         | ±10   | μΑ       |

| VIHTTL      | Input Voltage, Logic HIGH (TTL)       |                                               | 2.0   |         |       | V        |

| VILTTL      | Input Voltage, Logic LOW (TTL)        |                                               |       |         | 0.8   | V        |

| VIHCMOS     | Input Voltage, Logic HIGH (CMOS)      |                                               | 3.5   |         |       | V        |

| VILCMOS     | Input Voltage, Logic LOW (CMOS)       |                                               |       |         | 1.5   | V        |

| VT+         | Schmitt Trigger Positive<br>Threshold |                                               |       | 3.0     |       | V        |

| VT-         | Schmitt Trigger Negative<br>Threshold |                                               |       | 0.8     |       | V        |

| Юн          | Output Current, Logic HIGH            |                                               |       |         | -2.0  | mA       |

| loL         | Output Current, Logic LOW             |                                               |       |         | 2.0   | mA       |

| Voн         | Output Voltage, HIGH                  | IOH = -2mA                                    | 2.4   |         |       | V        |

| VoL         | Output Voltage, LOW                   | I <sub>OL</sub> = 2mA                         |       |         | 0.4   | V        |

| Analog In   | puts                                  |                                               | ,     |         |       |          |

| CAI         | A/D Input Capacitance                 | ADCLK = LOW<br>ADCLK = HIGH                   |       | 4<br>12 |       | pF<br>pF |

| RIN         | A/D Input Resistance                  |                                               | 500   | 1000    |       | ΚΩ       |

| ICB         | A/D Input Current                     |                                               |       |         | ±15   | μА       |

| VRO         | Voltage Reference Output              | Internal Reference                            | 0.988 | 1.235   | 1.482 | V        |

| IRO         | VREF Output Current                   | External VREF                                 | -150  |         | +150  | μΑ       |

| Analog Ou   | utputs                                |                                               |       |         | •     |          |

| Voc         | Video Output Compliance               |                                               | -0.4  |         | 2     | V        |

| Rout        | Video Output Resistance               |                                               |       | 15      |       | ΚΩ       |

| Cout        | Video Output Capacitance              | C <sub>OUT</sub> = 0 mA,<br>Frequency = 1 MHz |       | 15      |       | pF       |

| los         | Short-Circuit Current                 |                                               | -20   |         | -80   | mA       |

| IILP        | Input Current, LOW with pull-up       |                                               | -100  |         |       | μΑ       |

# **Switching Characteristics**

| Parameter |                                             | Conditions  | Min.   | Typ. <sup>1</sup> | Max.   | Unit |

|-----------|---------------------------------------------|-------------|--------|-------------------|--------|------|

| Clocks    |                                             | 1           |        | !                 | !      |      |

| fXTAL     | Crystal/Reference Clock Frequency           |             |        | 27                |        | MHz  |

| fXTOL     | Crystal/Reference Clock Frequency Tolerance |             |        | 50                |        | ppm  |

| tPWH      | Reference Clock Pulse Width, HIGH           |             |        | 18.5              |        | ns   |

| tpWL      | Reference Clock Pulse Width, LOW            |             |        | 18.5              |        | ns   |

| Syncs     |                                             | •           |        |                   |        |      |

| fH        | VGAHS Frequency                             | 60 Hz Modes | 30.840 | 31.469            | 32.100 | KHz  |

|           |                                             | 50 Hz Modes | 30.630 | 31.250            | 31.880 | KHz  |

| NH        | Lines per VGA frame                         | 60 Hz Modes |        | 525               |        |      |

|           |                                             | 50 Hz Modes |        | 625               |        |      |

|           |                                             | Tolerance   |        |                   | ±0     |      |

| tpwhs     | VGAHS Pulsewidth                            |             | 2      |                   |        | μs   |

| t∨s-HS    | VGAVS to VGAHS Delay                        |             | 0      |                   |        | ns   |

| tDS       | Sync Delay (VGA Sync to Sync Out)           |             |        | 100               |        | ns   |

| Video C   | Output                                      | -           | •      |                   |        |      |

| tDOV      | Analog Output Delay (PXCK Out to Video Out) |             |        |                   | 15     | ns   |

| tR        | D/A Output Current Risetime (10% to 90%)    |             |        | 2.2               |        | ns   |

| tF        | D/A Output Current Falltime (90% to 10%)    |             |        | 2                 |        | ns   |

| SKEW      | D/A to D/A Skew                             |             | -3     | 0                 | 3      | ns   |

| Control   | s                                           |             | •      |                   |        |      |

| tPWH      | Control Input Pulse Width, HIGH             |             |        | 50                |        | ns   |

| tpwL      | Control Input Pulse Width, LOW              |             |        | 50                |        | ns   |

| Micropi   | ocessor Interface                           |             |        |                   |        | !    |

| tPLCS     | CS Pulse Width, LOW                         |             | 12     |                   |        | ns   |

| tPHCS     | CS Pulse Width, HIGH                        |             | 8      |                   |        | ns   |

| tsa       | Address Setup Time                          |             | 2      |                   |        | ns   |

| tHA       | Address Hold Time                           |             | 4      |                   |        | ns   |

| tSD       | Data Setup Time                             |             | 7      |                   |        | ns   |

| tHD       | Data Hold Time                              |             | 2      |                   |        | ns   |

| tDOZ      | Output Delay, CS to low-Z                   |             | 4      |                   |        | ns   |

| tном      | Output Hold Time, CS to high-Z              |             | 9      |                   |        | ns   |

| tDOM      | Output Delay, CS to Data Valid              |             |        |                   | 40     | ns   |

<sup>1.</sup> Values shown in Typ column are typical for  $V_{DD} = V_{DDA} = +5V$  and  $T_A = 25^{\circ}C$ .

# **System Performance Characteristics**

| Paramete | er                                           | Conditions                                 | Min | Typ <sup>1</sup> | Max | Unit       |

|----------|----------------------------------------------|--------------------------------------------|-----|------------------|-----|------------|

| A/D Conv | verter Input                                 |                                            | !   | !                | !   |            |

| ELI      | A/D Integral Linearity Error,<br>Independent | VRT = 0.7V                                 |     | ±1               |     | LSB        |

| ELD      | A/D Differential Linearity Error             | VRT = 0.7V                                 |     | ±1               |     | LSB        |

| EAP      | Aperture Error                               |                                            |     | 30               |     | ps         |

| Еот      | Offset Voltage, Top                          | RT – VIN for most positive code transition | -20 | 45               | 80  | mV         |

| ЕОВ      | Offset Voltage, Bottom                       | VIN for most negative code transition      | 30  | 65               | 110 | mV         |

| D/A Conv | verter Output                                |                                            |     |                  |     |            |

| RES      | D/A Converter Resolution                     |                                            | 9   | 9                | 9   | Bits       |

| dp       | Differential Phase                           | PXCK = 27 MHz,<br>40 IRE Ramp              |     | 0.5              |     | degree     |

| dg       | Differential Gain                            | PXCK = 27 MHz,<br>40 IRE Ramp              |     | 1.5              |     | %          |

| PSRR     | Power Supply Rejection Ratio                 | CBYP = 0.1 $\mu$ F, f = 1 KHz              |     | 0.5              |     | %/<br>%VDD |

<sup>1.</sup> Values shown in Typ column are typical for  $V_{DD} = V_{DDA} = +5V$  and  $T_A = 25^{\circ}C$ .

# **Applications Discussion**

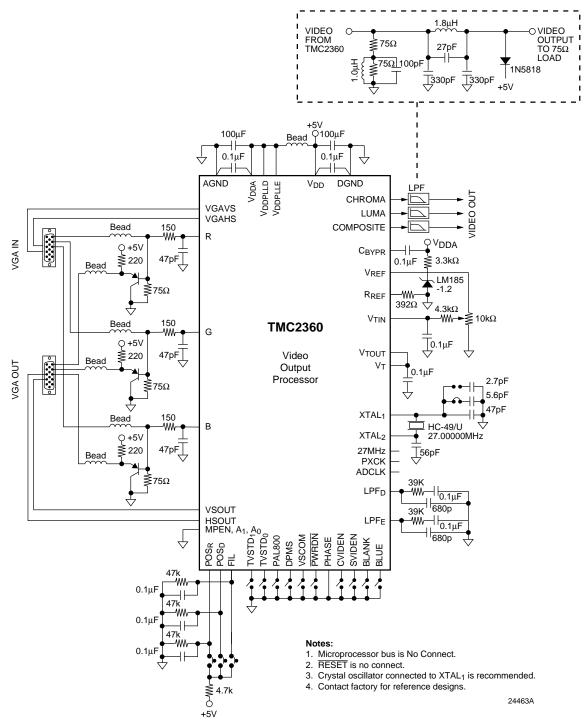

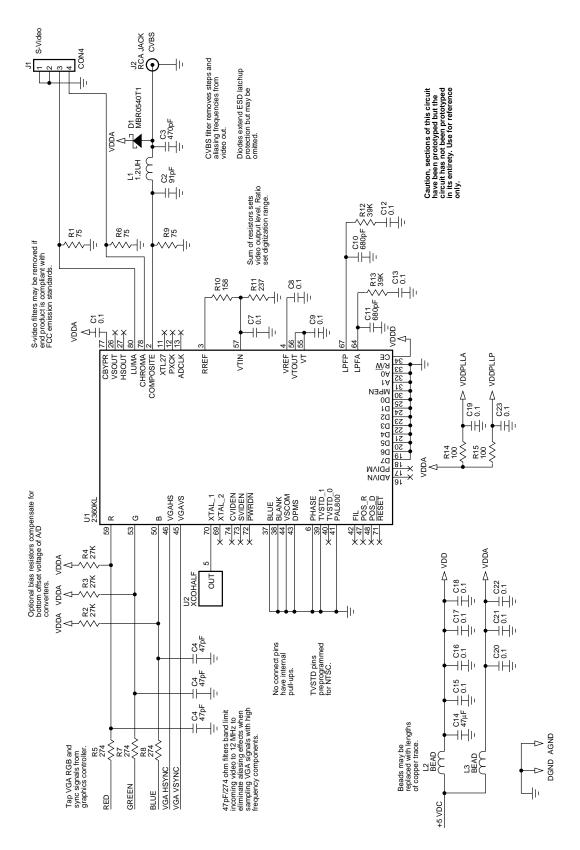

### **Applications Circuit**

Two applications circuits are shown. Figure 15 is the standard applications circuit. Figure 16 is a simplified circuit that exploits many of the internal features of the TMC2360.

The standard applications circuit is intended for third party add-on modules that interface a PC to a TV. Emitter followers buffer the VGA RGB signals so that VGA monitor disconnect does not impact the level of the TV image. Reference clock source is a crystal which requires tuning. A clock oscillator is recommended. VREF and VTIN are derived from an external voltage reference with an adjustment potentiometer.

Although intended for VGA controller applications, the simplified circuit embodies many techniques that can be exported to other applications. Bandwidth of the incoming RGB signals is limited to 12 MHz to equalize intensities of parallel vertical lines. Pull-up resistors compensate for the bottom offset voltages of the A/D converters. RREF is comprised of two series resistors which divide down the voltage for VT. Sinx/x filters are omitted since with 2x oversampling, losses are small (~ 1 dB). A low pass equiphase filter in the CVBS channel cuts HF transients for vectorscope measurements. PLL power is derived from two separately filtered sources.

#### Grounding

Analog and digital circuits are separated within the TMC2360. To keep digital system noise from the A/D and D/A converters, it is recommended that power supply voltages ( $V_{DD}$  and  $V_{DDA}$ ) originate from the same low-noise source, and that ground connections (DGND and AGND) be made to the analog ground plane. Power supply connections should be individually decoupled at each pin. Digital circuitry deriving input from the TMC2360 should be referred to the system digital ground plane.

#### **Printed Circuit Board Layout**

Designing with high-performance mixed-signal circuits demands printed circuits with ground planes. Overall system performance is strongly influenced by the board layout. Capacitive coupling from digital to analog circuits may result in poor A/D conversion. Consider the following suggestions for layout:

- Keep the critical analog traces as short as possible and as far as possible from all digital signals. Locate the TMC2360 near the board edge, close to the analog input/output connectors.

- 2. The power plane for the TMC2360 should be separate from that which supplies the rest of the digital circuitry. A single power plane should be used for all of the VDD pins. If the power supply for the TMC2360 is the same as that of the system's digital circuitry, power to the TMC2360 should be decoupled with ferrite beads and 0.1µF capacitors to reduce noise.

- The ground plane should be solid, not cross-hatched.

Connections to the ground plane should have very short leads.

- 4. Decoupling capacitors should be applied liberally to VDD pins. Remember that not all power supply pins are created equal. They supply different circuits on the integrated circuit, each of which generate varying amounts and types of noise. For best results, use 0.1μF ceramic capacitors. Lead lengths should be minimized. Ceramic chip capacitors are the best choice.

- 5. If the digital power supply has a dedicated power plane layer, it should not be placed under the TMC2360, the voltage reference, or the analog inputs. Capacitive coupling of digital power supply noise from this layer to the TMC2360 and its related analog circuitry can have an adverse effect on performance.

The 27 MHz clock reference or crystal should be handled carefully. Jitter and noise on this clock will degrade performance. With an external clock, the line should be terminated to eliminate overshoot and ringing.

Locate phase locked loop components close to the relevant TMC2360 pins. Isolate these components from noise.

Figure 15. Typical application circuit with internal phase-locked loops

Figure 16. Simplified Applications Circuit

# **Suggested User Instructions**

For a product incorporating the TMC2360, part of the documentation is expected to include operating instructions describing the functions of the TMC2360 user controls. A recommended text fragment follows.

Three external controls may be used to:

- position the image within the boundaries of the TV screen.

- 2) control vertical resolution.

Each control is a button that can be momentarily depressed to execute one cycle of the selected function.

#### **Position Controls**

Position controls shift the viewed image horizontally or vertically to reveal portions of the image that are located near the edges or in the overscan areas. At power-up, the default position is the midpoint of the adjustment range.